Рефераты по коммуникации и связи

Рефераты по косметологии

Рефераты по криминалистике

Рефераты по криминологии

Рефераты по науке и технике

Рефераты по кулинарии

Рефераты по культурологии

Рефераты по зарубежной литературе

Рефераты по логике

Рефераты по логистике

Рефераты по маркетингу

Рефераты по международному публичному праву

Рефераты по международному частному праву

Рефераты по международным отношениям

Рефераты по культуре и искусству

Рефераты по менеджменту

Рефераты по металлургии

Рефераты по налогообложению

Рефераты по оккультизму и уфологии

Рефераты по педагогике

Рефераты по политологии

Рефераты по праву

Биографии

Рефераты по предпринимательству

Рефераты по психологии

Рефераты по радиоэлектронике

Рефераты по риторике

Рефераты по социологии

Рефераты по статистике

Рефераты по страхованию

Рефераты по строительству

Рефераты по схемотехнике

Рефераты по таможенной системе

Сочинения по литературе и русскому языку

Рефераты по теории государства и права

Рефераты по теории организации

Рефераты по теплотехнике

Рефераты по технологии

Рефераты по товароведению

Рефераты по транспорту

Рефераты по трудовому праву

Рефераты по туризму

Рефераты по уголовному праву и процессу

Рефераты по управлению

Курсовая работа: Високотемпературні надпровідні схеми інтегральних мікросхем

Курсовая работа: Високотемпературні надпровідні схеми інтегральних мікросхем

Содержание

Вступ

1. Принцип дії SFQ цифрових схем

2. Основні проблеми в HTS SFQ ланцюгів

2.1 Параметри ланцюга

2.1.1 Джозефсонівські переходи

2.1.2 SFQ Петлі

2.1.3 Опір

2.2 Фактори, що обмежують HTS SFQ ланцюгових операцій

2.2.1 Теплові шуми

2.2.2 Паразитична Індуктивність

2.3 Виготовлення SFQ схем

2.3.1 Матеріали

2.3.2 Джозефсонівські переходи

2.4 Елементарні RSFQ схеми

2.4.1 Збалансований компаратор

2.4.2 Дільники напруги

2.4.3 Аналого-цифрові перетворювачі флеш типу

2.4.4 Підрахунок типу АЦП

2.4.5 Сігма-дельта АЦП

2.4.6 Колектор

2.4.7 Затримка лінії пам’яті

Висновки

Список використана література

Вступ

Надпровідникова цифрова схема має дві переваги в порівнянні з її конкурентоспроможністю, такі, як джозефсонівські і надпровідникові лінії електропередачі. Джозефсонівськ можуть перемикатися при нульовій напрузі протягом декількох пікосекунд потужність дисипації перемикання є вкрай низькою, так як напруга менша ніж на декілька мілівольт. Надпровідникова мікросхема ЛЕП здатна передавати пікосекундні сигнали практично на будь-яку відстань між чіпами зі швидкістю, близькою до швидкості світла.

Було витрачено багато зусиль для розробки схем з перевагами для вивчення надвисокої швидкості обробки систем надпровідних цифрових схем з використанням металевих матеріалів, надпровідників, таких як Pb і Nb. Два приклади таких зусиль: проект IBM (1969-1983) (1) і японського проекту MITI (1981-1991) (2). Успішна демонстрація на низькій Тс надпровідникових (LTS) каналів були зроблені, наприклад, 4Кбіт оперативної пам'яті, має 42000 вузлів і працює на частоті 620 МГц (3) комп'ютерного ланцюгового зв'язку логіки, має 4300 вузлів і працює на частоті 2 ГГц (4). Однак, стало ясно, що перше покоління надпровідних цифрових схем, так звані "замок логіки "схем з використанням нульового і кінцевого значення, напруга логічного" 0 "і" 1 ", не може конкурувати з високою швидкістю напівпровідниково схеми після охолодження. Основним недоліком "замка логіки" є те, що синхронізація великої радіочастоти (РЧ) поточного зовнішнього чіпа. Частота операцій обмежується кількома гігагерц, оскільки велика кількість поточних (наприклад, кілька ампер) не можуть бути поставлені на більш високій частоті. Багато уваги, таким чином, були спрямован на один потік квантів (SFQ).

Алгоритм, який кодує інформацію, не бінарний за допомогою постійного струму напруги, а за допомогою одного кванта магнітного потоку (Ф0=h/2e=2.07*10-15Wb). Надпровідні цифрові схеми з використанням програми SFQ були спочатку запропоновані Накаджімом і Онодером і в 1976 році (5), і з 1985 року значно покращилися в Московському державному університеті (6). Їх SFQ схем, називаються швидкі одно потокові квантові (RSFQ) схеми, стали одні з найпопулярніших SFQ схем , як очікувалося, працювали на частоті більше 100ГГц. Деякі високошвидкісн RSFQ схеми на основі тунельного типу LTS Джозефсонівських переходів не було, і у вищій мірі важливим з них аналого-цифрові перетворювачі, які були зроблені

А.Л. Семеновим та іншими з тисячами переходів працювали на частоті до 11ГГц (7).

ВТНП (HTS) цифрових схем, більше підходять для використання в SFQ схем, ніж ті, LTS, тому що HTS джозефсонівських природно змінених, це означає, що їх ВАХ не виявляють гістерезис, і в ланцюгах SFQ повинні бути переходи. Тунелем типу LTS джозефсонівські переходи, з іншого боку, від них і вимагають деяких опорів між двома електродами кожного переходу. Це робить характерну напругу (IcRn продукт) значень нижче, що дозволяє знизити швидкість роботи, а також ускладнює планування і процес виготовлення. Продукт з IcRn HTS переходах можна очікувати більшого, ніж у переходах, оскільки LTS нерозривно залежить від розриву напруги надпровідників. Кількість випробування схеми RSFQ з допомогою HTS джозефсонівських переходів не надходило, але більшість схем малими, тому що технологія виготовлення для HTS переходів і раніше знаходиться в первісному стані.

1. Принцип дії SFQ цифрових схем

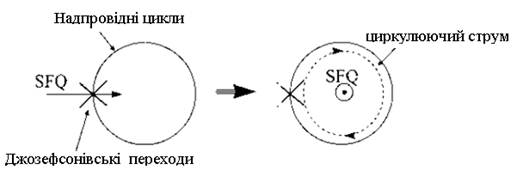

Магнітний потік квантів в надпровідних пристроях замкнутого циклу з мінімальним SFQ. На рис.1 показана найпростіша петля для замикання SFQ, для надпровідників, включаючи джозефсонівські. Як для магнітного потоку надпровідного переходу свинцю заборонено ефект Джозефсона Мейснера перехід грає роль "воріт" для виходу з петлі. Коли Джозефсонівських контактів вимикачів на напругу, магнітний потік іде

![]() Рис.1. Зберігання

SFQ в тому числі надпровідних джозефсонівських петель через з'єднання.

Рис.1. Зберігання

SFQ в тому числі надпровідних джозефсонівських петель через з'єднання.

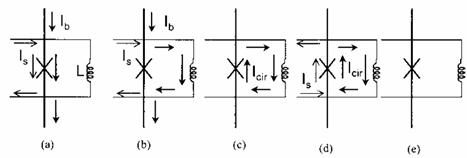

Якщо продукт від перехрестя критичного струму Ic і петлі індуктивності L від Ф0 <LIc < 2Ф0, тільки SFQ може існувати в цьому цикл після перезавантаження переходу в надпровідний стан і робить SFQ циркулюючого струму в Icir циклу. Рис.2. показує інше пояснення SFQ зберігання та випуску в надпровідних циклах. При постійному струмі зміщення Ib подається в надпровідникових петлях у тому числі переходу Джозефсона, майже всі нинішні переходи через індуктивність L в іншому рисунку (рис.2a). Тут, Ib менше ніж критичний струм Ic переходу. Якщо сигнал струму в подальшому використовується для з’єднання сумів, Ib і Is більше Ic, з'єднання перемикається напруга Ib і Is чи потік через ндуктивність (рис.2b). Після переходу в надпровідний стан Іb і Is перетворюється, поточний протікає через індуктивності зберігається в петлю (рис.2c). Збережений поточний Icir дорівнює Ф0/L якщо L і Ic значення задовольнять умову Ф0 < LIc < 2Ф0. Збереження Icir в циклі відповідають SFQ. Icir звільнений Is, в зворотному напрямку. Струми Is і Icir додалися тому що вони течуть в тому ж напрямку, і їх сума перевищує Ic (рис.2d).

Рис.2. Основн операції SFQ воріт.

Рис.3. Ряд схем SFQ: DC / SFQ, JTL, і SFQ / DC.

Потім включається і Icir розсіюється на переході (рис.2е). Це відповідає SFQ виходу з циклу. Рис.9.3 показу ряд схем SFQ: DC / SFQ трансформатор, Джозефсонівська (лінія електропередачі) ЛЕП (JTL) і SFQ / DC трансформатори. DC / SFQ перетворювач, який складається з переходів J1 і J2 та індуктивності L1, да мпульс SFQ на постійному струмі введення Iin. Якщо Iin збільшується за попереднє значення, імпульсу SFQ створюється по J2 включення і передається в правильному напрямку, на рис.3. DC / SFQ трансформатор скидається в початковий стан, коли Iin падає нижче певного значення. Скидання схеми супроводжується генерацією мпульсу SFQ через J2, не поширюються праворуч. JTL складається з трьох надпровідних петель у тому числі переходів J3-J5 й індуктивності L2-L4. Оскільки значення Ic і L і для кожного надпровідника контур менший, ніж в Ф0 в JTL, імпульсу SFQ поширюється через JTL без зберігання в цих петлях. SFQ / DC перетворювача містить цикл SFQ зберігання J5, L5, і L6, в якому LIc значення ЛІК більше Ф0, і зчитування SQUID, що складається з переходів J7 і J8 і напруги на виході терміналу між ними.

З цієї схеми відхилення постійного струму Ib показано на рис.3, ВЧ зміщення необхідне для поточної схеми для їх скидання непотрібних операцій в SFQ схем. Це головна причина того, SFQ схеми набагато швидші, ніж запірн схеми. Будь-які логічні функції та операції з пам'ятю можуть бути реалізован SFQ використанням схем, комбінуючи LIc > Ф0 петлі і LIc < Ф0 петель.

У схемах SFQ, двійкової інформації поширюється як дуже короткі напруги імпульсів замість постійної напруги в надпровідні запірні схемі, а також у всіх напівпровідникових схем. Імпульсну напругу V (T) має квантова область:

![]()

Швидкість перемикання τ від простої SFQ петлі як і на рис.1-3 обмежена характерними частотами змінного струму ефект Джозефсона. Використання критичних струмів джозефсонівських контактів мікросхеми та нормального опору Rn, ми можемо представити τ наступним чином:

![]()

IcRn величина є одна з найбільш важливих параметрів для оцінки Джозефсонівських переходів, які використовуються в схемах SFQ. Якщо продукт IcRn становить 1 мВ, який розумн значення для HTS джозефсонівських переходів, τ може складати всього лише 2шт.

Енергоспоживання на одне перемикання джозефсонівських SFQ про вихід Ic2Rnτ = IcФ0 і що необхідні при переході на частоті ƒ є nIcФ0ƒ коли кількість переходів Джозефсона на виході є n. Використання таких типових значень як Ic = 0,4 мА та n=4, ми можемо оцінити спожиту потужність HTS SFQ схеми з частотою 100 ГГц до 0,33 µW. З іншого боку, споживання енергії з метал-оксидного напівпровідника (C-MOS) на вході 3 В рівень сигналу 7-fF ємність 62 µВт, навіть якщо його робочі частоти тільки 1 ГГц. Таким чином, споживання енергії на виході HTS SFQ на два порядки менше, ніж величина виходу C-MOS.

2. Основні проблеми в HTS SFQ ланцюгів

2.1 Параметри ланцюга

2.1.1 Джозефсонівські переходи

Над затуханнями джозефсонівських переходів, які мають dc кривих I-V, не гістерезису, використовуються в схемах SFQ. Розподільні загасання представлені βс= (2π/Ф0) IcRn2C де C переходом ємності (8,9). Nb / AlОx / Nb джозефсонівських контактів (10), що використовуються в LTS SFQ схемах тунельні переходи з своїм βс набагато більше, ніж 1. Тому, βс з точки з'єднання повинен бути скорочений шляхом додавання через її опір тунельного бар'єру (6). Опір шунта використовується в так званих “NEC стандартних процесів” є 3-5 Ω (11). Додавання шунтів опором знижує IcRn значення на 4,2 K від 1,7 мВ до 0,3 мВ подовжує час перемикання від 1,2 до 6,7 пс. З ВТС джозефсонівських контактів, з іншого боку, це менше 1 без додаткового опору шунта. Це відбувається тому, що ВТС на тунельних переходах, мають слабкі зв'язки і, отже, характеризуються меншими значеннями Rn. Внутрішні IcRn значення HTS джозефсонівських можна очікувати більшого, ніж LTS переходи через велик енергетичні щілини у HTS матеріалів. Розвиток покращеної якості джозефсонівських переходів з високими IcRn значеннями є одним із самих важливих питань в галузі досліджень, пов'язаних з додатками HTS SFQ ланцюга. Спад краю HTS переходів за допомогою Ga-легованих PrBa2Cu3Ox бар'єру і мають IcRn значення від 8 мВ при 4,2 K було повідомлено групою університету Твенте (12) і спад краю HTS переходах допомогою Со-легованого YBa2Cu3Ox, бар'єр і, IcRn значення 0,8 мВ при 65 K були зареєстровані в групі Northrop Grumman (13).

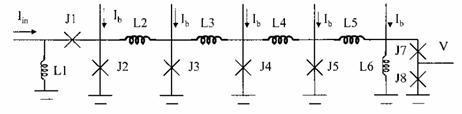

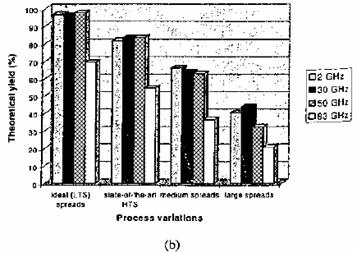

Розглядаються відносини між Ic поширення в чіп і рівня схеми інтеграц (14,15). Щоб проілюструвати ефект критичного струму користуються схемою виходу, ми вважаємо один перехід входу критичного струму Ic. Крім того, ми передбачаємо, що процес виготовлення дасть переходам, розподіл критичного струму розподіл Гауса з стандартним відхиленням σ.

Вірогідність даного переходу, що входять Δ край надано критичного струмами розподілу Гауса зі стандартним відхиленням:

Критичний струм кожного з'єднання в ланцюзі, що складається з N таких переходів повинен бути між Ic-Δ і Ic+Δ. Сумарний вихід ланцюга буде PN. Рис.9.4 показує, цінність, необхідних у виробництві ланцюгів даного з'єднання (15). Маленький критичний струм розповсюдження досягнутих на сьогоднішній день складає 1σ =8% для 100 спаду краю переходів модифікованим інтерфейсом бар'єр (16). Як показано на рис.4, де критичний струм поширення відповідає прибутковості 50% для схем з кілька сотень вузлів.

Розповсюдження від Rn і IcRn продукт має менше за критичне значення, ніж схема поширення Ic. Крім того, розповсюдження Rn IcRn продукту, як правило, менше, ніж поширення Ic (17).

2.1.2 SFQ Петлі

SFQ схеми містять два види петель SFQ. Одним з них є для зберігання циклу, для якого Ф0 < βl = LIc < 2Ф0. Інша передача циклу для JTL, для яких βL < Ф0. Ц типові значення 1,5 Ф0 і 0,5 Ф0, відповідно. Тут L ндуктивність петлі SFQ і Іс критичний струм переходу у тому циклі.

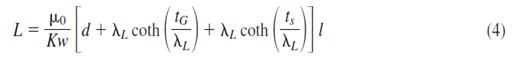

Індуктивність L надпровідного мікролінійний рядок якого, що розділ представлений на рис.5 дається

де w - ширина лінії, L - довжина лінії, L є надпровідна глибина проникнення поверхнею грунту і лінія, tG tc товщини поверхні грунту та лінії, відповідно, d є товщина ізоляції шару, µ0 проникність вільного простору, і К окантовка (1). Тому що λL матеріалів HTS більше, ніж матеріали LTS, L на квадратний (L) значення для HTS мікрополоскових ліній більше, ніж для Nb мікрополоскових відповідно до тієї ж товщини діелектрика.

Важко викласти невелику петлю L з-за великого значення L. Більше того, ми пояснимо докладно в розділі 9.3.2.1., Ic не може бути зменшений занадто багато через тепловий шум. Труднощі рішення менших βL петля є однією з найсерйозніших проблем в HTS схеми SFQ.

2.1.3 Опір

Три види опору необхідні в чіпі HTS SFQ. Опір менше кілька Ом розміщуються в деяких в SFQ. Деякі SFQ виходи не мають потреби в цих малих опорах, але деякі використовуються для затухання опору (6) і Сигма-дельта модулятор, який використовується для основної частини свого роду аналого - цифровий трансформатор, є необхідними для опору.

Надпровідникові

Надпровідникові

![]()

|

![]()

|

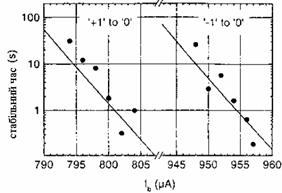

Рис.5. Поперечний переріз надпровідних мікрополоскових прямих над надпровідної заземленою поверхнею.

Опір використовуватися для розділення струму зміщення в кожному циклі SFQ паралельно має значення кілька десятків Ом. Цей опір, необхідний для запобігання несправних операцій, викликаних поточним відображенням з інших включених переходів. Третій вид опору відповідні опору у високошвидкісних I / O лінії. Він необхідний для повного опору на 50-Ω зовнішньої сигнально лінії.

2.2 Фактори, що обмежують HTS SFQ ланцюгових операцій

2.2.1 Теплові шуми

На жаль, цифрових схем на основі Nb необхідно охолоджувати до температури рідкого гелію. Використання матеріалів HTS дозволить скоротити витрати на охолодження, а також підвищення робочих частот з-за більш високого IcRn HTS Джозефсонівських контактів, але більш висока робоча температура призводить до більш теплового шуму. Енергетичний бар'єр між двома станами потоку на виході SFQ є дуже низьким. Груба оцінка (18) показує, що для типового критичного струму близького до 10-4 А, цей енергетичний бар'єр близький до 10-1J. Таким чином, на деякі коливання, не враховуються оцінки на виході, описаних у попередньому розділі, можуть збільшити спонтанного перемикання потоку. Ймовірність виходу SFQ, викликані тепловим шумом були досліджено теоретично й експериментально.

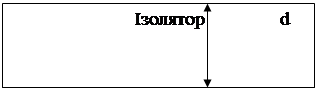

Збалансованого компаратора з допомогою двох переходів (рис.9.6) є основним компонентом з RSFQ логічних вентилів і SFQ підрахунку аналого-цифровий перетворювач (6). Державний університет Нью-Йорку група (18-21) досліджували вплив теплових шумів на виході SFQ теоретично на основі аналізу діяльності збалансованого порівняння. Коли на зовнішні виходи драйвер посилає імпульс SFQ збалансованому

Рис.6. Еквівалентна схема збалансованого компаратора.

компаратору, один з вузлів вимикання. Який переключає з'єднання шляхом додаткового поточного Ix подається в центральний вузол пристрою. J2 вимикачі коли Ix>0 і J1 вимикачів, коли Ix <0. Однак неминучим створенням коливань, сірі зони навколо Ix =0, де кожен з вузлів, має ймовірність 0 < P (Ix) < 1 бути включеним. Ефективна ширина ΔIx цього сірі зони, які визначається як ΔIx= (dp/dIx) - 1| p=1/2, зменшує параметр кулуарів RSFQ логічних елементів. Результати ц теорії є приблизно такими:

![]()

де It = (2e/ћ) kBT ≈ (0.042 µA) * T (K) і Т температура. У теплових межах коливань, ћ (kωс) 1/2 << kBT.

В ншому випадку, квантова межа, темпи залежності відрізняється,

![]()

тепловий потік групи, якій замінюється поточною квантовою одиницею IQ = (2e/ћ) eIcRn. Без обліку теплової та квантових флуктуацій, збалансований компаратор працює зазвичай 0 < Ix/Ic < 1. Операції різниц стають вузькими в результаті коливань. Операція детермінованих полів показана на рис.9.4 повинна бути переглянута з урахуванням цих шумів.

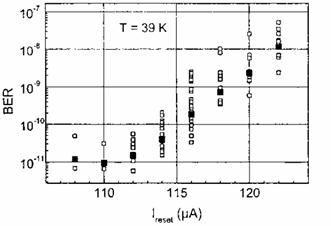

Сетчел (22) і Джеффрі та ін. (23) імітованих коефіцієнтів помилкових бітів (BER) різних SFQ воріт, і їхн результати знаходяться в добрі згоді з теоретичними передбаченнями.

Сетчел дійшов до висновку, що для роботи при температурах вище 40 К можлива тільки для тих схем, які мають добру перенесеність шуму, і Джефрі уклав що провал транспортного переключення (Т-FF) робоча температура повинна бути не нижче 40 К в порядку похибки менше 10 ГГц на 10-6 швидкостей.

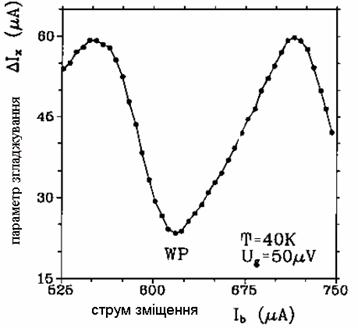

Вивчено вплив теплових шумів на збалансований компаратор з бікрісталом джозефсонівських експериментів (24), співвідношення між струмом зміщення та Δix виміряні при 40 К показана на малюнку 9.7. ΔIx / Ic відношення з різними умовами упередженості оцінюється від 6% до 17%. Статична помилка відбувається, коли петля SFQ втрачає зберігання кванта потоку з-за теплового шуму і статичний коефіцієнт помилок петлі SFQ зберігання виготовлений з HTS бікрісталом джозефсонівських переходів вимірювали Чонг та ін. (25). Конфігурації стека двох HTS DC SQUIDs використана в цьому експерименті, одна виступає як сховише петлі для квантів потоку та інші, що виступає в якості зчитування потоку стану зберігання SQUID. Стабільні вимірювання часу для обох “+I" -I" SFQ в зберіганні циклу поблизу порога струму зміщення показані на рис.8. зменшення близько 6-7µA струму зсуву збільшиться стабільний час одного порядку.

Рис.7. Залежність Ix та струму зміщення, б.

Неправильне підключення вимикачів на своєму етапі відповідь на вхідний імпульс SFQ (26). Ці динамічні помилки домінуючими.

Рис.8. Вимірюється час стабільним для обох “+1" і “-1”станів поблизу струму зміщення. Суцільні лінії показують результати модельних розрахунків.

Рис.9. Білі квадрати виміряних точок; чорні квадрати відповідно середні значення.

Над практичними схемами RSFQ. Збалансований компаратор, що складається з орієнтованої зони випромінювання опромінено пучком на переходах використана в цьому експерименті. Рис.9.9 показує, BER залежності від прикладеного струму, який так само, як Ix. Температура у цьому експерименті 39 К вхідний імпульс SFQ частоти близько 1 ГГц. Були отримані BER менш 10-11, показуючи, що SFQ схема може працювати при 39 К. Їх вимірювання також вказували, що значне полів параметрів схеми повинні бути прийняті до уваги коли температура вище 4,2 К.

Підтримання постійного поля шумів при підвищених температурах Ic значень переходу до збільшення частки до робочої температури і схеми індуктивності для зменшення значень, зберігаючи βL постійною. Довге проникнення в глибину матеріалів HTS, однак, робить такі мало індуктівні значення недоцільними. Крім того, значення Іс, ймовірно, буде обмежено до 0,4 мА. Схеми повинн або бути обмежені порівняно з низькою робочою температурою або працювати з меншою.

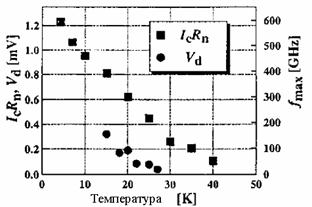

Максимальна напруга Vd розділені за RSFQ Т-FF визначає максимальну частоту операції βmax в TFF: βmax =Vd/Ф0. Значення IcRn джозефсонівських переходів в Т-FF і Vd цього Т-FF були зіставлені та їх температурна залежність була розглянута Сайто та ін. (27). Температурні залежності значень IcRn показані на рис.10. Vd ясно менше, ніж значення IcRn, хоча їх температурних залежностей достатньо подібні.

Рис.10. Залежність значення IcRn і напруги Vd.

Максимальна Vd на 15K, ƒmax відповідає 155 ГГц. Оцінка обмеження факторів, що визначаються як ƒmax = γIcRn/Ф0, становить 0,4 > γ >0,1 для 15 K < Т < 27 К. Передбачається, що тепловий шум впливає на Т-FF операції, і вони включають такі теплов шуми в їх моделювання схеми. Результати моделювання і експериментальн результати, погоджені досить добре. Ці результати показують, що тепловий шум впливає на Т-FF логіку функціонування пригнічує максимальні частоти. Вони припустили, що джозефсонівські контакти, для яких IcRn більше, ніж 1 мВ необхідні, щоб операція по швидкостях понад 100 ГГц і повинні бути отримані на 30 К.

2.2.2 Паразитична Індуктивність

Паразитарна ндуктивність неминуча в практичному організаційному макеті джозефсонівських переходах і контактах в SFQ цифрових схем. Лінія індуктивності в ланцюгах є HTS вдвічі більша, ніж в схемах LTS. Крім того, дрібні елементи індуктивності HTS використовувалися в схемах з підтримкою βl их Ic. Таким чином, більш серйозна проблема для HTS схеми SFQ ніж LTS схем.

Сатчел (22) і Джефрі (23) імітували паразитний вплив індуктивності до схеми виходу, а також теплового шуму. На рис.11, моделювання за результатами Jeferry, в якому дало результати для Т-FF SFQ з різними умовами та експлуатацією частот описані з (рис.11а). Ці результати показують, що кількісна паразитична ндуктивність може мати значний вплив на ймовірність отримання HTS SFQ схема працює на надвисоких швидкостях.

Рис.11. Монте-Карло дають результати для Т-FF (а) і (б) без паразитичних індуктивностей.

Значення цієї паразитичної індуктивності достатньо велике, щоб скоротити операційний семплер ланцюга.

2.3 Виготовлення SFQ схем

2.3.1 Матеріали

Надпровідник, який найбільш широко використовується в HTS цифрових схемах Yba2Cu3Ox (YBCO). YBCO плівки можуть бути вирощені: SrTiO3 (STO), MgO, LaAlO3, NdGaO3, YSZ (стабілізований оксидом ітрію діоксиду цирконію), Sr2AlTaO6 (СБ), Sr 2AlNbO6 (SAN), і (La0.3Sr0.7) (Al0.65Ta0.35) Ox (останній). Серед них, СТО досі найбільш популярний матеріал підкладки для SFQ цифрових схем, оскільки його постійна решітки і коефіцієнт теплового розширення близькі до YBCO. Вибір надпровідників у підкладці обмежує вибір ізоляторів. Вкрай бажано, що ізолятор може бути виготовлено з використанням тих же матеріалів, які використовується для депозитів YBCO і при температурі не набагато вище. Очевидним вибором для ізоляторів є субстрати матеріалів. Існують шари MgO, LaAlO3, NdGaO3,SAN. Опір цих матеріалів достатньо високим для цифрового ланцюга.

Серед них, Pd / Au був з набагато меншим температурним коефіцієнтом опору, особливо при низькій температурі, ніж Pd. Поверхневий опір 400-нм Pd / Au. Було близько 0.6Ω від 4.2 К до 77 К. Вони припустили, що Pd / Au є найбільш підходящим матеріалом для схем SFQ. Форрестер та ін. Au використовуватися для резисторів з адгезією Ti шар в Sigma дельта модулятор (31) і Мо був використаний для 1 - Ω резистора Міллер та ін. (32). Контактний опір між цими резистора і шару YBCO є небажано великим у порівнянні з опором листа, тому важливо, що будуть досліджені способи зниження опору контакту.

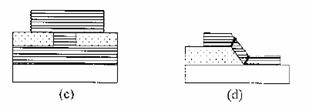

2.3.2 Джозефсонівські переходи

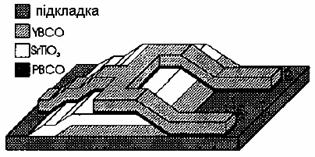

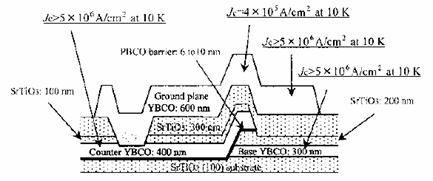

З різних видів джозефсонівських ступенів розвитку, EDGE-тип переходів (34), схематично показано на рис.12а, як видається, є найбільш перспективними для цифрової схеми через свої невелик розміри, потенційна керованість переходу критичного струму і перехід значень опору, і простота надпровідних проводів.

Рис. 12 Схема перетину HTS джозефсонівських переходів.

Сато та ін. Розробив на місці крайній підготовки до рампи PbCO-сходження ребер набув поширення Ic 1σ=10% за 12 переходів з продуктом IcRn 2 мВ при 4,2 К (35). Co-легованих YBCO діє як бар'єр при температурі вище 50 К і 20-рампа сходження ребер з співголовами легованих бар'єрів, які зроблені Малісоном та ін. Був продуктом IcRn 0,3 мВ при 50 К і показав Ic поширення 12% (1) (36). Інші краї перехрестя з Co-легованого бар'єр YBCO, база якого містить електроди YBCO 5% La, виставлена IcRn продукти 0.5 - 0.8 мВ при 65 К з 1σ Iс що поширюється вниз до 12%, повідомив Хант та ін. (13). Було встановлено, що Ga допінгу, Rn систематично збільшився, а Ic залишився незмінним. Ванговен та ін. Доказали, що шляхом легування Ga, IcRn продукція була збільшена до 8 мВ при 4,2 К (12).

Інтерфейс нженерії рамп-сходження ребер (IEJ), розроблена Moeckly та ін. (37) привертають велику увагу, тому що відтворений виготовлення цілком підходить для додатків цифрової схеми. У цьому процесі осадження бар'єр формується тільки шляхом структурної зміни за допомогою іонного бомбардування і вакуумного відпалу. Зміни, в якому був сформований нормальний фрезерних іон. Їх зміна пов'язана в переходах (MIJ) також показала, відтворення lc з 1σ поширення в lc складає менше 8% на 100 контактів (16).

Недоліком використання рамп-сходження ребер в ланцюгах SFQ є те, що буде важко зменшити петлю індуктивності. Один зі способів зменшити індуктивність SFQ циклу за допомогою вертикальної структури. Вертикальна петля може бути побудована за допомогою Stacked переходів (рис.12b) і з віссю Microbridge (CAM) в переходах (рис.12c). Як і конфігурація Stacked переходів, що й у Nb / Alox / Nb переходах, які використовуються в схемах LTS SFQ, розвиток Stacked переходів для HTS схеми SFQ довелось чекати від першого етапу HTS перехід розвитку. Нещодавно Stacked з продуктом IcRn 2,1 мВ і 10% lσ поширив ІМС на 4,2 K. Ц характеристики подібні від краю рампи перехрестя і є перспективними у зв’язку з SFQ схем застосування.

CAM просто надпровідною структурою без навмисного формування бар’єру слабкого зв’язку. З’єднання між двома шарами YBCO. Це поєднання має IcRn продукт, як великий 1,2 мВ при 60 К. Однак, оскільки критичного струму в звичайних (2 -μм-діаметр) CAM технології занадто високі. CAM діаметр 0,5 м потрібно для цілей критичного струму 0,5 мА на 40 - 60 К (39). Здається, що для досягнення гарно однорідності Ic буде важко завдяки своїй невеликій території.

Крок від краю межі (SEGB) вузлів, які утворюють розриви в кристалічній орієнтації, охоплює HTS крок у підкладці (рис.12d), більш легко інтегруються в мультислоях ніж рампа-сходження ребер (32,40). Орієнтовані-електронно-променево-опроміненн (ОЕПО) переходи на одному шарі YBCO визначаються шляхом опромінення краю з високими дозами електронів, що робить їх чисто резистивними. Таким чином, була можливість для точного визначення різних критичних струмів для переходу ОЕПО (41). ОЕПО переходи не підходять для використання у великих масштабах схеми, оскільки занадто багато опромінення часу потрібно для прийняття кожного переходу. Кілька HTS цифрових схем виготовлені з використанням зернограничних переходів, як виготовляються шляхом здачі на зберігання епітаксіального YBCO на бікристал підкладки (42), тому що вони мають порівняно великі IcRn. Використання бікристаллом зернограничних переходів обмежені в невеликих масштабах.

З метою реалізації високопродуктивних HTS SFQ схем, розробка схеми процесу, якої інтегрує відтворення джозефсонівських в епітаксіальних мультислоях ма важливе значення. Зокрема, надпровідність землі індуктивність коливального контуру потрібно тримати досить низькими, щоб імпульс SFQ міг генерувати достатній струм у навантаження і індуктор βL в циклі SFQ можуть бути розроблені в рамках діапазону.

Першим на доповідь виготовлення переходів над SEGB землі був Missert (43). Цей пристрій діє як SQUID тільки до 20 К. Операц температури SQUID, яка складалася з переходів SEGB з 200k землі збільшена до 77К вище, Форестер та ін. (44). Вони виміряли температурну залежність L знайшли її в добрій згоді з теорією, згідно з якою температурна залежність проникнення представляє глибини, використовуючи формулу Казимира, λ (t) = λ0/ [1- (T/Tc) 4] 1/2, де λ0 це глибина проникнення при Т = 0.

Рамп-сходження ребер з 450-нм. SQUID звернення працюють на температурах до 50 K, на використані товщі землі під площину робить поверхню бази електрода YBCO грубішою, в результаті чого появляється надлишковий струм в рампі-сходження ребер.

Co-легованих YBCO / YBCO переходах більше 200 нм YBCO площині. Обидва шаруватої структури, окрім тієї ж, що Аль Хант ET. Використовували La-легованого YBCO за базовий Mallison електрод і ін. SAN використовували для ізолятора. Хант та ін. Повідомили L□ 1,0 рН і великим IcRn продукти 0.5 - 0.8 мВ при 65 К. Mallison повідомив L□ 1,2 рН при 70 К. Ці заходи індуктивностей є досить низькими, щоб почати Highspeed

Тести малого масштабу схеми, навіть нижче, індуктивності L□ = 0,8 рН. Як і в структурі, показаній на рис.13, базовий електрод YBCO в структурі виступає як YBCO. Таким чином, ця структура не вимагає додаткові площини землі. Така ж структура використана в роботах.

CAM технології, які використовуються природним наслідком низької індуктивності:

Рис.13 Креслення DC SQUID

Рис.14 Схематичний перетин YBCO / PbCO / YBCO. Рампа краю переходу інтегрована з верхньою площиною земл "HUG структури".

Описан вище літаки землею поховані під переходах, і Товщина поховали літаки земля була бути нижче 200 нм, оскільки товщі землі привели в літаках більше шорсткість поверхні, що дозволило знизити якість з’єднання. Кожен шар YBCO структури HUG було перевірено на тісні поточні щільності до рівня asgrown YBCO плівки. Опір тришарових по 400-нм плівка товщиною STO виміряна більше 1 мΩ в діапазон від 4.2 К до 300 К на площі 100*100 μm, що є достатнім для автоматичних операцій. Високотемпературні процеси використані у формуванні площини грунту не впливають на якість з'єднання, такі як IcRn продукти та надлишковий струм. Структура температурних залежностей може бути встановлена шляхом полосковою моделлю. Ця модель дещо відрізняється від Кортер-Казимира форми, λ (t) = λ0/ [1- (T/Tc) 2] 1-2.

2.4 Елементарні RSFQ схеми

Кілька простих схем RSFQ виготовлені і випробувані на низьких частотах у порядку для перевірки основних операцій SFQ зберігання потоку і перевірки застосовності конкретного виготовлення.

Першим продемонстрував роботу схеми HTS SFQ Іванов (50), який продемонстрував роботу схеми, що складається з усічених скидань - набір (RF) фліп-флоп (FF) (без переходу в буфер скидання каналу) доповнюються за необхідних вхідних і вихідних ланцюгів, використовуючи граничні переходи в YBCO тонкої плівки. Використання LTS (свинцевого сплаву) в площині землі, має обмежену схему операції до 4,2 К.

Форрестер та ін. Повідомили про два простих етапи зрушення з магнітним READ поєднанні SQUID, як показано на рис.16a (51). Ця схема одноярусна YBCO з п'ятьма SEGB переходами. Рисунок показує, що 16b - зсув резистора завантажений і Shifted SFQ дані по команді на 65 К. Відзначимо, що існує помилка близько 130 х років, коли потік квантово зміщується у відсутності зсуву команди. Хоча ефективність зв'язку між читанням SQUID і першими даними SQUID були лише близько 4%, як зберігання та їх SFQ руху у відповідь на сигнали застосовуються в ланцюзі HTS.

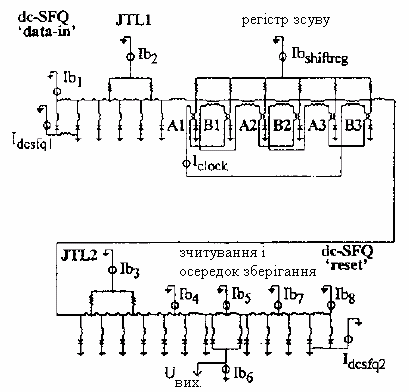

RSFQ серія, яка включає два DC / SFQ перетворювачі, два JTLs, повна

RS-FF, SFQ / DC перетворювача, було реалізовано в площині джозефсонівських переходах утворена FEBI. Низькочастотні тестування показали, що це DC схемою працю надійно на 30 К, на кілька градусів нижче ефективної критичної температури переходу. Тризмінному розряді SFQ що складається з регістра зсуву, DC / SFQ, одного зчитування SQUID, яке виступає в якості SFQ / DC конвертор, і три JTLs (Рис.17) Схема складається з 26 бікристалів Джозефсонівських контактів, що найбільшим числом в будь-якій розвиненій схемі HTS до теперішнього часу, належного функціонування всіх компонентів схеми була підтверджена низькою частотою тестування на 50 К. оперативної схеми.3% для годинника поточних і 5% для струму зміщення в регістр зсуву.

Рис.16 Схема для двох етапів зареєстрованих зрушень і (б) зміна реєстрація завантаження і Shifted SFQ даних по команді на 65 К. Зверніть увагу на помилку в 130 С.

Ц вузькі поля можливо обумовлені значним поширенням критичних струмів в джозефсонівських переходах. Після зміщення струми встановлені, то помилки спостерігалися протягом 2-х періодів виміру.

RS-FF з 16 переходів CAM виступив Херст і ін. і працював на 45 K (39). Його конструкція була аналогічна повідомив раніше Шохор ін. (52). CAM переходи мають переваги, які роблять їх особливо придатними для прийняття вертикальних петель SFQ з низькою індуктивністю та зменшенням паразитних індуктивностей. Кім та ін. перевірили діяльність RS-FF з чотирма бікристалами перехресть, 71 K (54). SFQ зберігається в RS-FF, було зачитано за допомогою магнітного зв'язку SQUID.

Рис.17 Еквівалентна схема трьох-бітного SFQ регістра зсуву.

2.4.1 Збалансований компаратор

Збалансований компаратор, в якому два джозефсонівських послідовних з'єднань, це не тільки один з важливих елементів ланцюгів RSFQ, один досліджує ймовірність перемикання джозефсонівських переходів. Отримані "параметри згладжування" перемикання "сірої зони" і BER з допомогою компаратора, відповідно, описаних у розділі 9.3.2.1 компаратор був частиною кільцевого генератора в тому числі 15 FEBI переходів (рис.18). SFQ може циркулювати в кільці осцилятора його поширення частот можуть бути розраховані, за відношенням Джозефсона, в залежності від напруги на кільцевому генераторі. Були отримані максимальн частоти стабільної циркуляції 6 ГГц. Це відповідає затримці 17пс за перехід.

Зонненберг

та інші випробовували збалансований компаратор в три-HTS-шаровій технології.

Вісім переходів індуктивності перебували на похилій горизонтальній площині, щоб

зменшити індуктивність значення (55). Правильного функціонування збалансованого

компаратора отримали шляхом постійного вимірювання властивостей перемикання.

Сіра зона перемикання вимірювалася в залежності від температури (4.2-30 K)

робочої частоти (2.5-80 ГГц). Для кожної температури, сіра ширина зони ма

мінімум при низьких швидкостях імпульс 10-15![]() , де Ic кожного переходу становить

близько 100

, де Ic кожного переходу становить

близько 100![]() . Ширина сірої зони збільшується зі збільшенням частоти

пульсу і збільшився більш швидкими темпами на 30 K ніж на 4,2 К.

. Ширина сірої зони збільшується зі збільшенням частоти

пульсу і збільшився більш швидкими темпами на 30 K ніж на 4,2 К.

Рис.18. Еквівалентні схеми кільцевого генератора SFQ зі збалансованим компаратором.

2.4.2 Дільники напруги

Окрем

елементи логічної схеми RSFQ можуть працювати на частотах для яких характерна частота

Джозефсона. Обмеження 0, коли багато цих елементів пов'язані один з одним за

допомогою JTL, і це призводить до необхідності використання джозефсонівських

контактів з вищими IcRn продуктивностями (56).

Високочастотні обмеження елементів RSFQ можуть бути експериментально знайден

за допомогою співвідношення Джозефсона між середньою напругою постійного струму

на переході і коливання Джозефсона частотою ![]() . T-FF проходить кожен другий вихор від входу до

виходу, так що вихідна напруга Vout це одна половина Vin.

Просте вимірювання Vin і Vout дозволяє перевірити

функціонування T-FF на високих частотах. Коли частотна межа не перевищена, Vout

буде рівна Vin / 2.

. T-FF проходить кожен другий вихор від входу до

виходу, так що вихідна напруга Vout це одна половина Vin.

Просте вимірювання Vin і Vout дозволяє перевірити

функціонування T-FF на високих частотах. Коли частотна межа не перевищена, Vout

буде рівна Vin / 2.

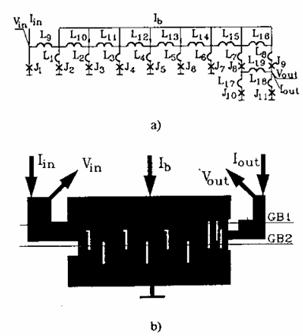

Каплуненко

та ін. Перші, хто провів випробування дільники напруги з використанням HTS

матеріалів. Вони використовували одношарові YBCO і своєрідний дизайн. Мал

ндуктивності контуру SFQ, близько 10 рН утворюють вузькі щілини шириною 0,4![]() , які можна порівняти з глибиною проникнення

, які можна порівняти з глибиною проникнення ![]() ~0,15

~0,15![]() зверхпровідної плівки YBCO. Дві щілини, розділені мостом

0,8

зверхпровідної плівки YBCO. Дві щілини, розділені мостом

0,8 ![]() , забезпечують міцний зв'язок між двома петлями SFQ

(58,59). Еквівалентна схема і макет Т-FF ланцюга, яка включала 11 бікристальних

вузлів, показані на рис. 19a і 19b. Як показана рис. 19c, функціонування

спостерігалося до 0,82

, забезпечують міцний зв'язок між двома петлями SFQ

(58,59). Еквівалентна схема і макет Т-FF ланцюга, яка включала 11 бікристальних

вузлів, показані на рис. 19a і 19b. Як показана рис. 19c, функціонування

спостерігалося до 0,82 ![]() при 4,4 K, даючи

при 4,4 K, даючи ![]() в межах точності експерименту, що відповідає частот

Джозефсона близько 400 ГГц.

в межах точності експерименту, що відповідає частот

Джозефсона близько 400 ГГц.

Дільник

напруги з допомогою дев'яти рамп краю переходів з шаруватої горизонтальній

площині був виготовлений Хасімото і ін. На 12,5K, максимальна напруга, при

якому ![]() Vвих 0.4

Vвих 0.4![]() . Це значення відповідає 200 ГГц. Сайто та ін. Сфабрикували

дільник напруги, використовуючи 11 типу рампи краю переходів і експлуатується

на частотах до 155 Ггц при 15 К і 19 ГГц при 27 K (27).

. Це значення відповідає 200 ГГц. Сайто та ін. Сфабрикували

дільник напруги, використовуючи 11 типу рампи краю переходів і експлуатується

на частотах до 155 Ггц при 15 К і 19 ГГц при 27 K (27).

Рис. 19 (а) Еквівалентна схема, (б) план, і (с), виміряні введення Vin, а також продукції, Vout, напруги дільника напруги на основ субмікронних щілин індуктивності.

2.4.3 Аналого-цифрові перетворювач флеш типу

Періодичний характер SQUID дозволяє будувати n-розрядний аналого-цифровий перетворювач флеш-типу (AD), перетворювач містить тільки n компараторів, а не 2n +1, що використовуються в напівпровідниках флеш-тип. Циркулюючим струмом в петлі SQUID періодична функція потоку, що застосовується з періодичністю Ф0. Це формує основу для 1 біт перетворювача. Динамічний діапазон такого перетворювача обмежується тільки, скільки магнітного потоку може бути застосований до SQUID без придушення критичних струмів джозефсонівських в тому числі. Відповідно до пропозиції К0, обсяг магнітного потоку може бути значно збільшений, з допомогою порівняння на основі квазі-одного-з'єднання SQUID (QOS).

Рис.

20 (a) показує, що еквівалентна схема основних QOS лежить в основі компаратора.

Як показано на рис. 20b, струм через оцифровування J0 переходу в

цьому ланцюзі є періодичною функцією аналогового вхідного струму Ia.

Критичний струм J0 повинен бути набагато меншим, ніж вибірка Js

переходу, якщо вплив Js на поведінку QOS повинний бути невеликим. L

з цього циклу має бути менше 1, оскільки періодична крива повинна мати одне

значення для всіх значень Ia. Для роботи високочастотних, значення ![]() повинно бути не менше 0.5. Для 4-бітних

перетворювачів, періодична крива повинна мати хоча б чотири повних періоди. При

дискретизації імпульсу Ip застосовується з належним чином закріплена

амплітуда ІС. Кожне перемикання результується вибірковим переходом в

напругу на виході вузла схеми, і цей стан вважається логічною "1".

Дискретизація імпульсу Ip, не призводять до вихідної напруги, стан вважається

логічним "0".

повинно бути не менше 0.5. Для 4-бітних

перетворювачів, періодична крива повинна мати хоча б чотири повних періоди. При

дискретизації імпульсу Ip застосовується з належним чином закріплена

амплітуда ІС. Кожне перемикання результується вибірковим переходом в

напругу на виході вузла схеми, і цей стан вважається логічною "1".

Дискретизація імпульсу Ip, не призводять до вихідної напруги, стан вважається

логічним "0".

Рис. 20 (а) Еквівалентна схема базового QOS періодичного компаратора і (б) періодичні залежності QOS поточного IJ0 на аналоговому струм Ia.

Про використання HTS матеріалів першим повідомив Wiegerink та ін. За їх схемою, два джозефсонівських переходи у QOS поділені на два паралельні ребра рампи, яка дозволяє реалізувати дуже низьку петлю індуктивності. Експлуатація цього компаратора продемонстрована на повільних швидкостях відбору проб, хоча згасання критичного струму переходу через магнітні поля, пов'язані з вхідним струмом Ia явно спостерігається. Поріг QOS поліпшені шляхом зміни його структури і до восьми повних періодів спостерігалися без згасання. При температурі близько 40K, кілька 4-бітних перетворювачів чіпів за допомогою вдосконаленої QOS повністю функціонували при роботі на низькій частоті (1 кГц).

Умедзава та ін. Також виготовили 1-бітовий QOS зі надпровідним циклом використання SEGB перехрестя і базові АЦ-перетворення показали, що при 77 K, він працював на частотах від 10 кГц до 1 МГц (64).

Збалансований компаратор описаний в розділі 9.4.2 також може бути використаний як компаратор флеш-типу. Кідіярова-Шевченко та ін. Сконструйовані таким чином перетворювач використані тришаровою HTS, а також змоделювали принцип його роботи.

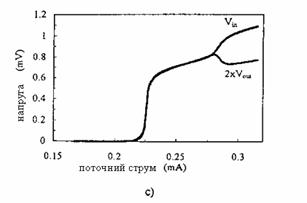

2.4.4 Підрахунок типу АЦП

Рис.21

показує, блок-схему підрахунку типу перетворювача. Керовані напругою осцилятори

(VCO) постійно стежать за аналоговим входом, створюючи імпульси зі швидкістю,

пропорційною напрузі. Змінний ефект Джозефсона в єдиний вузол дає майже

деальний перетворювач "напруга - частота", тому що співвідношення

Джозефсона дає ![]() . Повний 12-бітний NbN AD перетворювач з допомогою цієї,

будови використовує тільки 52 джозефсонівських переходів.

. Повний 12-бітний NbN AD перетворювач з допомогою цієї,

будови використовує тільки 52 джозефсонівських переходів.

SFQ

лічильника показано на рис.21 і складається з серії SFQ T-FFs. Маккамбрідж та

н, зробили перший крок на шлях до створення розрахунку АЦП, виготовлення

випробування одного T-FF з DC / SFQ конвертер, JTL та зчитування воріт.

Маккамбрідж та ін. використовували три шари YBCO структури, в якій 10 рамп краю

переходів із легованого YBCO бар’єру на похилій площині землі YBCO були

використані. Їх схема працювала на 65 K. При низьких швидкостях. Схема НД

складалася з 14 рамп краю переходів шаруватої структури, такою ж, як і переходи

в ланцюзі Маккамбрідж. Зчитування напруги ланцюга ЗС показує, що при 65 K IcRn,

було вище, ніж 0,1 ![]() .

.

2.4.5 Сігма-дельта АЦП

Сігма-дельта

![]() архітектури є кращими архітектурами для АЦП з

високим динамічним діапазоном. Цей підхід передискретизації здійснюється

напівпровідниковими приладами, що використовуються в додатках, де аудіо сигнали

на кілогерц частоти дискретизації МГц частот

архітектури є кращими архітектурами для АЦП з

високим динамічним діапазоном. Цей підхід передискретизації здійснюється

напівпровідниковими приладами, що використовуються в додатках, де аудіо сигнали

на кілогерц частоти дискретизації МГц частот ![]() модулятора і результуючий потік бітів цифрово

фільтрації, щоб забезпечити врегулювання 18 - 20Біт. Напівпровідниковий

модулятора і результуючий потік бітів цифрово

фільтрації, щоб забезпечити врегулювання 18 - 20Біт. Напівпровідниковий ![]() AD перетворювач обмежується МГц проб і цифровою

фільтрацією. Надпровідник

AD перетворювач обмежується МГц проб і цифровою

фільтрацією. Надпровідник ![]() AD, однак, може виконувати гігагерц відбору проб

застосовувати переваги цифрової фільтрації, МГц смуги пропускання сигналів.

Крім того, потік квантування в надпровідниковому контур забезпечує точний

квантово-механічний механізм зворотного зв'язку. Точність відгуку дуже важлив

для виконання

AD, однак, може виконувати гігагерц відбору проб

застосовувати переваги цифрової фільтрації, МГц смуги пропускання сигналів.

Крім того, потік квантування в надпровідниковому контур забезпечує точний

квантово-механічний механізм зворотного зв'язку. Точність відгуку дуже важлив

для виконання ![]() AD перетворювачів.

AD перетворювачів.

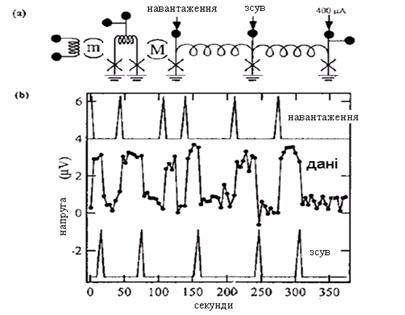

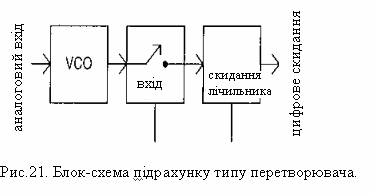

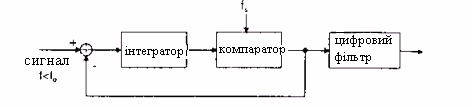

Рис.22

показує, блок-схему першого порядку ![]() AD модулятора. Цифровий сигнал знімається з вхідного

сигналу в ланцюзі зворотного зв'язку. Цей вид зворотного зв'язку приводить до

усередненого виході компаратора в точності вхідного сигналу. Відхилення

квантованих виходів компаратора від аналогового вхідного сигналу може бути

небезпечним, як шум і називається шумом квантування. Шум квантування зміщений в

область високих частот. Очевидно, що відношення сигнал шум може бути покращене

шляхом фільтрації частот вищої смуги сигналу.

AD модулятора. Цифровий сигнал знімається з вхідного

сигналу в ланцюзі зворотного зв'язку. Цей вид зворотного зв'язку приводить до

усередненого виході компаратора в точності вхідного сигналу. Відхилення

квантованих виходів компаратора від аналогового вхідного сигналу може бути

небезпечним, як шум і називається шумом квантування. Шум квантування зміщений в

область високих частот. Очевидно, що відношення сигнал шум може бути покращене

шляхом фільтрації частот вищої смуги сигналу.

Інтегратор,

компаратор і зворотний зв'язок першого порядку ![]() модулятор легко реалізується за допомогою

джозефсонівських контактів, як показано на Рис.22. Форрестер та ін.

Сфабрикували простий HTS

модулятор легко реалізується за допомогою

джозефсонівських контактів, як показано на Рис.22. Форрестер та ін.

Сфабрикували простий HTS ![]() модулятор. Вони вимірювали свої виступи на 35K шляхом

введення 5,01 МГц сигналу і передачі вихідного потоку бітів аналізатором

спектру, яким виміряно відносну амплітуду небажаних гармонік, і визначальних

шпорів вільного динамічного діапазону (SFDR). З частотою дискретизації 27 ГГц,

SFDP виміряно понад 75 дБ. Ця величина порівнянна з модулятором LTS.

модулятор. Вони вимірювали свої виступи на 35K шляхом

введення 5,01 МГц сигналу і передачі вихідного потоку бітів аналізатором

спектру, яким виміряно відносну амплітуду небажаних гармонік, і визначальних

шпорів вільного динамічного діапазону (SFDR). З частотою дискретизації 27 ГГц,

SFDP виміряно понад 75 дБ. Ця величина порівнянна з модулятором LTS.

Рис.22

Блок-схема першого порядку ![]() модулятора з цифровим фільтром.

модулятора з цифровим фільтром.

Про

нший HTS ![]() модулятор повідомив Рук та ін. Схема виготовлена на

підкладці бікристала STO. YBCO / STO / YBCO тришарових виготовлена методом

лазерного напилення.

модулятор повідомив Рук та ін. Схема виготовлена на

підкладці бікристала STO. YBCO / STO / YBCO тришарових виготовлена методом

лазерного напилення.

Самий нижній шар служить надпровідною поверхнею грунту і джозефсонівські переходи сформовані у верхньому шарі. Pd / Au, ця тонка плівка використана для нтегратора опору.

Ланцюг складається з DC / SFQ конвертер, JTL, компаратор, L / R інтегратора і вихідних каскадів, що складалися з 10 вузлів. Коректної роботи модулятора було підтверджено на постійному струмі 34 К. лінійності модулятора, і досліджено шляхом вимірювання гармонійних спотворень 19,5 кГц синусоїдального сигналу, а мінімальну роздільну здатність 5 біт може бути оцінена записаного спектру.

Така точність обмежена шумом підсилювача. Коректна робота струмової петлі зворотного зв'язку продемонстрована шляхом розрізання зворотної індуктивності.

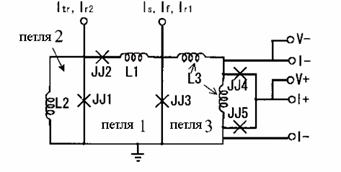

2.4.6 Колектор

Вс описані вище схеми елементів, що складалися з великих схем RSFQ або AD перетворювачів, за винятком осцилятора кільця і дільників напруги, які були реалізовані для дослідження операцій з частотами схеми SFQ. Ці самі схеми, не можуть бути поставлені на застосування. Колекторна схема складається з п'яти рамп краю переходів з накопичуючою горизонтальною площиною і спирається на операції SFQ. Зміна інтерфейсу переходів та верхнього шару грунту площини (HUG структури) застосовані в процесі виготовлення. На рис.23 показана схема дизайну колекторного ланцюга. SFQ імпульс струму Ip породжується JJ1 і JJ2 в момент зростання струму Іtr, і цей імпульс відправляється JJ3, де він з'єднується з сигналу струму (T) і зворотнім зв'язком поточного Iƒ, який в даний момент визначається генератором Ip. Коли сума перевищу три ступені порогового значення, SFQ зберігається в надпровідниковому контурі, який містить JJ3 і L3. Потім, збережена SFQ викликає вихідну напругу при зчитування SQUID, який складається з JJ4 і JJ5. У кінці кожного циклу вибірки, що зберігається SFQ в контурі скидання використовуються негативні скидання струмів Ir.

Рис.23 Схема підключення колектора HTS.

Значення

![]() (IS), яке визначається як мінімальний

(IS), яке визначається як мінімальний ![]() , необхідне для зберігання SFQ в цьому циклі для Is,

яке може бути визначене, повторивши зазначені вище операції зі значеннями

різних

, необхідне для зберігання SFQ в цьому циклі для Is,

яке може бути визначене, повторивши зазначені вище операції зі значеннями

різних ![]() . Порівняння

. Порівняння ![]() (IS) з

(IS) з![]() , яка є

, яка є ![]() для IS =0, ми можемо отримати Is (t)

значення. Сигналу вимірюється за допомогою виявлення Is (t),

значення для різних генераторів Ip.

для IS =0, ми можемо отримати Is (t)

значення. Сигналу вимірюється за допомогою виявлення Is (t),

значення для різних генераторів Ip.

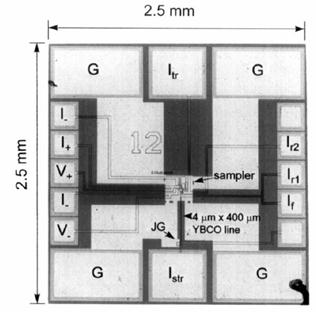

Рис.24 показує зразок чіпа для вимірювання високих частот роздільною здатністю. Чіп відносно невеликим (2,5 мм квадратних), так що високошвидкісних ліній струму на підтримку STO (який має величезний діелектричної проникності) не вистачає. Сигнал струму заміряти цей зразок генерується сигнал входу по струму на Істр на чіпі Джозефсона сигналу генератора (СГ) і поширюється на зразок через 4 - му масштабі, 400 - м в довжину лінії без YBCO підходящу опору.

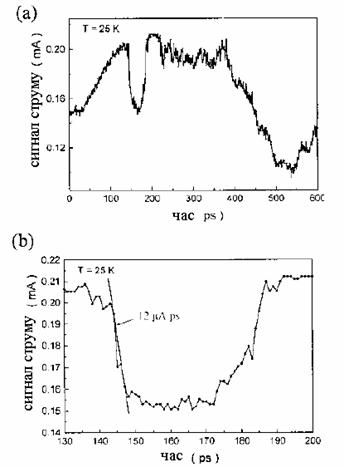

Рис.25 показаний один з результатів з 1-пс час затримки між кожною точкою відбору проб. Падіння структури близько 160 пс на рис.25a був переоцінюються в деталях показано на рис.25b. На рис.25b, максимальна диференціальних час вимірюється сигнал в 12 /пс, який впав 60 з 5-пс проміжок часу з 2,5µA - чутливістю по струму.

Семплер HTS здатний вимірювати струм сигналів безпосередньо з піко- і мікроампер резолюцій. Напівпровідникових проб і електрооптичних (НЗ), семплери, добре відомі для характеристики тимчасово форми високошвидкісних електричних сигналів. Тим не менше, напівпровідникові пробовідбірники виміру напруги і E-O пробовідбірники дотримуватися електричного поля. Для вимірювання струму використанням цих проб, електричного імпедансу виміряних частин повинен бути відомий. Як робочої частоти великих напівпровідник ГГц вимірювання.

Рис.24. Крупним планом оптичні HTS семплери чіпа. Семплер схеми в центрі і нижче семплер на генератор джозефсонівського сигналу.

Збільшується з точки зору проектування схеми та електромагнітної сумісності (EMC) технології. Однак через опір проводки в LSI тестованого, як правило, невідомі з-за своєї складної шаруватої структури і ще через струм, що протікає через проводку не може бути виміряна за допомогою напівпровідникових або EO пробовідбірників. Семплер HTS здатний спостерігати ток БІС з високою роздільною здатністю. Ми очікуємо, що HTS семплер дуже корисні для вивчення деяких перехідних явищ, перехресних перешкод і EMC в високошвидкісних БІС.

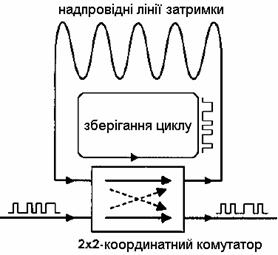

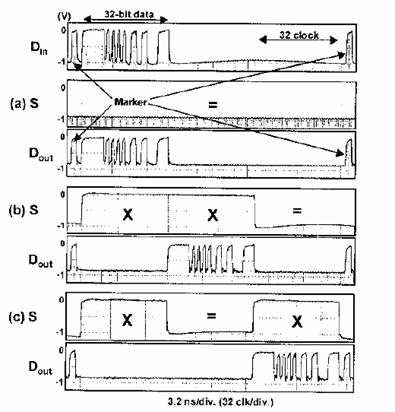

2.4.7 Затримка лінії пам’яті

Хаттор нші розробила пам’яті HTS на лініях затримки для асинхронного режиму передачі (ATM) системи комутац (74). Ця пам'ять сама по собі не цифрова схема, вона має цікаві застосування цифрових пристроїв ВТНП. Це пристрої з високошвидкісними напівпровідниковими перемикачами.

Рис. 25. Поточні сигнали вимірювання HTS проб: (А) сигналу вимірюється від 0 до 600 пс і (б) оцінка сигналу між 130 пс і 200 пс.

Швидке зростання трафіку в області телекомунікацій призвела до необхідності швидких систем комутацій. Межа частоти дано системи визначається за максимальною тактовою частотою звичайного напівпровідникового пристрою пам'яті. Тому, що максимальна частота цих зареєстрованих файлів обмежена за поширенням затримка між кожною стадією реєстрації. Оскільки надпровідних ліній затримки пам'яті дозволяє уникнути цього обмеження використання аналогово затримки задається надпровідною лінією затримки, ця пам'ять повинна бути використана у високій швидкості банкомату буферної пам'яті.

Рис. 26. Конфігурація лінії затримки пам’яті. Ця пам’ять складається з надпровідної лінії затримки і 2*2 координатний комутатор.

Конфігурація повторної лінії затримки пам'яті показано на рис.26. Пам'ять рециркуляції зберігання петлі для фіксованої довжини пакетної передачі даних і складається з надпровідної лін затримки і напівпровідникового 2*2 координатного комутатора. Ця затримка дає лінію введення даних фіксованого затримкою, відповідає його довжині. Координатний дозволяє перехресне або паралельне з'єднання між двома вхідними портами і двома портами виводу. Лін затримки зворотнього зв'язку з вихідним портом до його вхідних портів і форми зберігання циклу. Це цикл має тривалість, яка відповідає фіксованій довжин пакетної передачі даних. Оскільки сигнали в лінії затримки не можуть бути посилені і реорганізовані, затухання та спотворення в лінії затримки повинні бути дуже низькими, незважаючи на високі частоти і довгострокові затримки. Це неможливо для плоскої лінії електропередачі із звичайного, з-за її поверхневого опору. Ось чому надпровідні лінії затримки використовували.

Компланарна затримка YBCO лінії 10м в ширину і 37см в довжину було сфабриковано. Ця лінія затримки була близько 2,8нс і були використані, поряд з комерційно доступними напівпровідникові інтегральн схеми, щоб зробити надпровідними пам’яті затримки на лініях. Як показано на рис.27, ця пам’ять працювала як 32-бітний буфер зберігання при тактовій частоті 10 ГГц при 46 K, яка у кілька разів швидше, ніж напівпровідникові реєстраційні файли. Цей результат показує, що надпровідні лінії затримки пам’яті є потужним кандидатом для високошвидкісних ATM зберігання буфера камери.

Рис.27 32-бітна ГГц буферизації експлуатація лінії затримки Пам’ять: (а) небуферизована пам’ять та (б) операції з буферизацією пакетів тривалістю (32 годин) і буферизація під час операц подвійної довжини пакета тривалістю (64годин).

Висновки

Інтегра́льна мікросхе́ма (рос. інтегральна микросхема, англ. integrated circuit, IC; нім. integral Mikroschema n) - мініатюрний мікроелектронний виріб, елементи якого нерозривно пов'язані конструктивно, технологічно та електрично. Виконує визначені функції перетворення і має високу щільність упаковки електрично з'єднаних між собою елементів і компонентів, як одним цілим з точки зору вимог до випробувань та експлуатації.

Топографія нтегральної мікросхеми (ТІМС, англ. Semiconductor intellectual property core, IP Core або Intellectual Property Rights on Integrated Circuit) - мікроелектронний виріб кінцево або проміжної форми, призначений для виконання функцій електронної схеми, елементи і з'єднання якого неподільно сформовані в об'ємі або на поверхн матеріалу, що становить основу такого виробу, незалежно від способу його виготовлення.

ТІМС є комплексним описом структури, функцій та взаємозв'язків компонентів архітектури електронно мікросхеми. Права на використання такої архітектури є інтелектуальною власністю певної особи. У минулому запропоновані наступні назви мікросхем у залежност від ступеня інтеграції (у дужках кількість елементів для цифрових схем):

МІС - мала нтегральна схема (до 100 елементів у кристалі);

СІС - середня нтегральна схема (до 1 000);

ВІС - велика нтегральна схема (до 10 000);

ЗВІС - зверхвелика нтегральна схема (до 1 мільйона);

УВІС - ультравелика інтегральна схема (до 1 мільярда);

ГВІС - гігавелик (більш 1 мільярда).

В даний час назва ГВІС практично не використовується (наприклад, останні версії процесорів Pentium 4 містять поки кілька сотень мільйонів транзисторів), і всі схеми з числом елементів, що перевищують 10 000, відносять до класу ЗВІС, вважаючи УВІС його підкласом.

Технологія виготовлення.

Напівпровідникова мікросхема - всі елементи і міжелементне з'єднання виконані на одному напівпровідниковому кристалі (наприклад, кремнію, германія, арсеніду галію).

Плівкова мікросхема - всі елементи і міжелементне з'єднання виконані у виді плівок:

товстоплівкова нтегральна схема;

тонкоплівкова нтегральна схема.

Гібридна мікросхема - крім напівпровідникового кристалу містить трохи безкорпусних діодів, транзисторів і інших електронних компонентів, поміщених в один корпус.

Основним елементом аналогових мікросхем є транзистори (біполярні чи польові). Різниця в технолог виготовлення транзисторів істотно впливає на характеристики мікросхем. Тому нерідко в описі мікросхеми вказують технологію виготовлення, щоб підкреслити тим самим загальну характеристику властивостей і можливостей мікросхеми. У сучасних технологіях поєднують технології біполярних і польових транзисторів, щоб домогтися поліпшення характеристик мікросхем.

Інтегральна мікросхема може володіти закінченим, як завгодно складним, функціоналом - аж до цілого мікрокомп'ютера (однокристальний мікрокомп'ютер).

Аналогові схеми.

Операційн підсилювачі;

Генератори сигналів;

Фільтри (у тому числі на пьєзоефекті);

Аналогов помножувачі;

Стабілізатори джерел живлення;

Мікросхеми керування імпульсних блоків живлення;

Перетворювач сигналів;

Цифрові схеми

Логічні елементи;

Тригери;

Регістри;

Буферн перетворювачі;

Модулі пам'яті;

Мікроконтролери;

(Мікро) процесори (у тому числі ЦПУ в комп'ютері);

Однокристальн мікрокомп'ютери;

Список використана література

1. W Anacker. Josephson computer technology: An IBM research project. IBM J Res Dev 24: 107-252, 1980.

2. H Kroger. Josephson devices and technology. In: Japanese Assessment. Park Ridge, NJ: Noyes Data Corporation, 1986, pp 250-306.

3. S Nagasawa, H Numata, Y Hashimoto, S Tahara. High-frequency clock operation of Josephson 256-word _ 16-bit RAMs. IEEE Trans Appl Supercond As-9: 3708-3713, 1999.

4. S Yorozu, Y Hashimoto, H Numata, M Koike, M Tanaka, S Tahara. Full operation of a three-node pipeline-ring switching chip for a superconducting network system. IEEE Trans Appl Supercond As-9: 3590-3593, 1999.

5. K Nakajima, Y Onodera. Logic gate of Josephson network. J Appl Phys 47: 1620-1627, 1976.

6. KK Likharev, VK Semenov. RSFQ logic/memory family: A new Josephson-junction technology for sub-terahertz-clock-frequency digital systems. IEEE Trans Appl Supercond As-1: 3-28, 1991.

7. VK Semenov, YA Polyakov, D Schneider. Implementation of oversampling analogto-digital converter based on RSFQ logic. Extended Abstracts of the 6th International Superconductive Electronics Conference, Berlin, Germany, H. Koch and S. Knappe, PTB, June 25-28, 1997, Vol.1, pp 41-43.

8. WC Stewart. Current-voltage characteristics of superconducting tunnel junctions. Appl Phys Lett 12: 277-280, 1968.

9. DE McCumber. Effects of ac impedance on dc voltage-current characteristics of superconductor weak-link junctions. J Appl Phys 39: 3113-3118, 1968.

10. M Gurvitch, MA Washington, HA Huggins. High-quality refractory Josephson tunnel junctions utilizing thin aluminum layers. Appl Phys Lett 42: 472-474, 1983.

11. H Numata, M Tanaka, Y Kitagawa, S Tahara. Investigation of SFQ integrated circuits using Nb fabrication process. Extended Abstracts of the 7th International Superconductive Electronics Conference, Berkeley, USA, T Van Duzer, June 21-25, 1999, pp 272-274.